mirror of

https://github.com/supleed2/ELEC50010-IAC-CW.git

synced 2025-01-04 03:02:00 +00:00

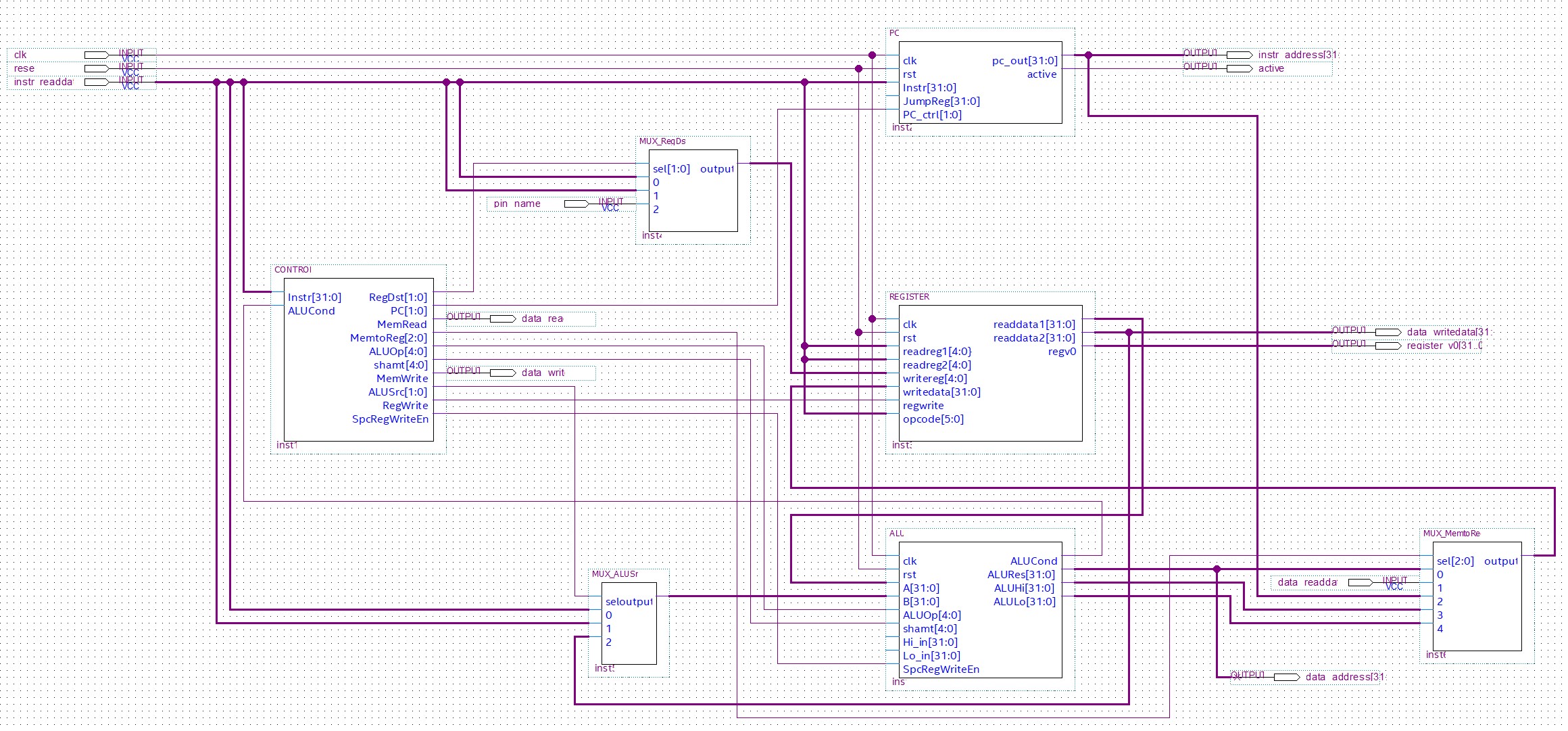

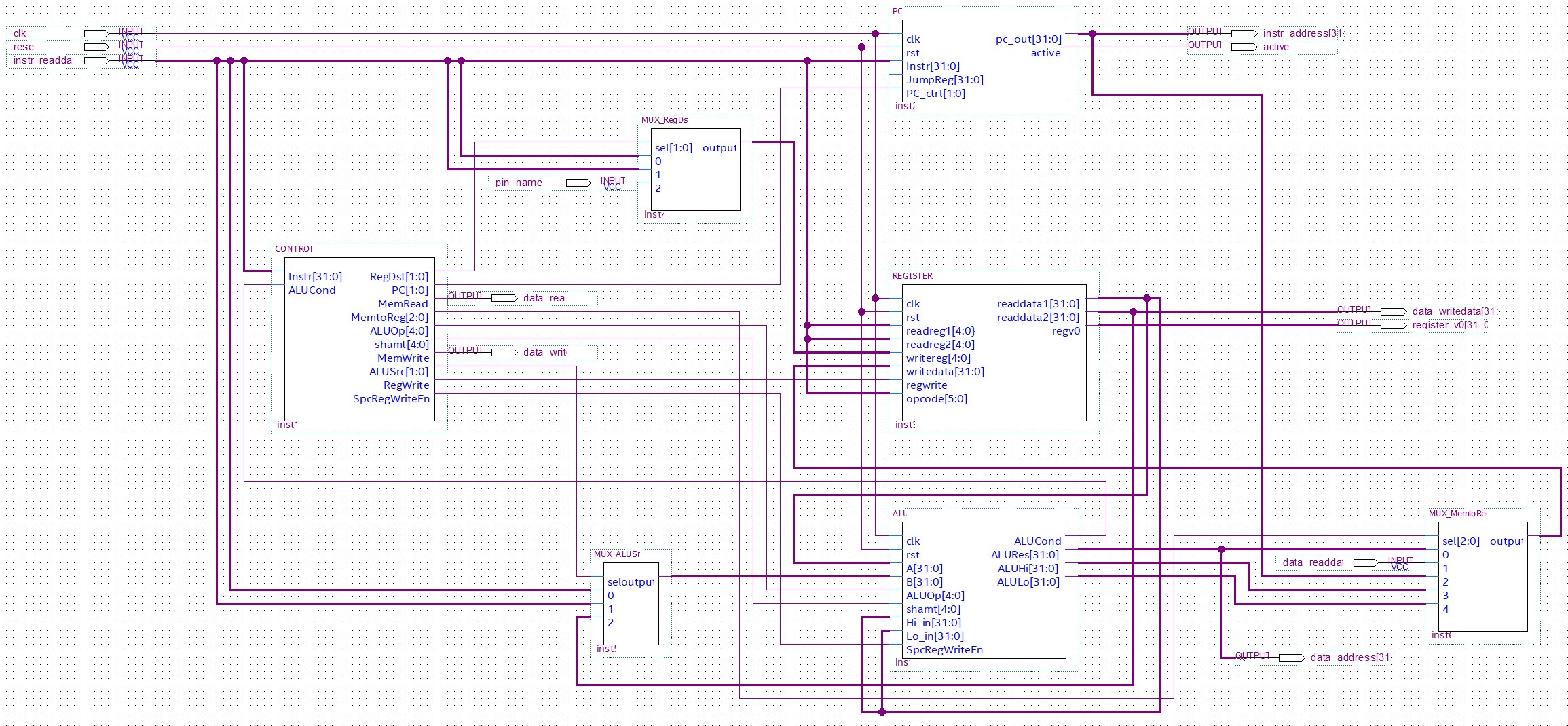

Added Diagram related files, and Datasheet update

This commit is contained in:

parent

3291163ed2

commit

8ec142585b

Quartus Diagram

ALU.bdfALU.bsfCONTROL.bdfCONTROL.bsfMIPS_CPU_Diagram.bdfMIPS_CPU_Diagram.psdMIPS_CPU_Diagram.qpfMIPS_CPU_Diagram.qsfMIPS_CPU_Diagram.qwsMUX_ALUSrc.bdfMUX_ALUSrc.bsfMUX_MemtoReg.bdfMUX_MemtoReg.bsfMUX_RegDst.bdfMUX_RegDst.bsfPC.bdfPC.bsfREGISTERS.bdfREGISTERS.bsfScreenshot 2020-12-20 152417.jpgScreenshot 2020-12-21 130927.jpg

db

docs

reference

230

Quartus Diagram/ALU.bdf

Normal file

230

Quartus Diagram/ALU.bdf

Normal file

|

|

@ -0,0 +1,230 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "graphic" (version "1.4"))

|

||||

(pin

|

||||

(input)

|

||||

(rect 160 80 328 96)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "clk" (rect 5 0 20 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 152 112 320 128)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "rst" (rect 5 0 17 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 176 496 344 512)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "SpcRegWriteEn" (rect 5 0 78 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 152 256 320 272)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUOp[4:0]" (rect 5 0 60 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 160 200 328 216)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "B[31:0]" (rect 5 0 39 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 152 144 320 160)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "A[31:0]" (rect 5 0 40 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 160 320 328 336)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "shamt[4:0]" (rect 5 0 56 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 160 384 328 400)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "Hi_in[31:0]" (rect 5 0 56 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 168 432 336 448)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "Lo_in[31:0]" (rect 5 0 59 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 584 128 760 144)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUCond" (rect 90 0 134 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 584 224 760 240)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALURes[31:0]" (rect 90 0 154 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 584 320 760 336)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUHi[31:0]" (rect 90 0 146 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 592 392 768 408)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALULo[31:0]" (rect 90 0 149 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

121

Quartus Diagram/ALU.bsf

Normal file

121

Quartus Diagram/ALU.bsf

Normal file

|

|

@ -0,0 +1,121 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "symbol" (version "1.2"))

|

||||

(symbol

|

||||

(rect 16 16 240 208)

|

||||

(text "ALU" (rect 5 0 21 10)(font "Tahoma" (font_size 6)))

|

||||

(text "inst" (rect 8 171 24 188)(font "Intel Clear" ))

|

||||

(port

|

||||

(pt 0 32)

|

||||

(input)

|

||||

(text "clk" (rect 0 0 16 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "clk" (rect 21 27 37 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 32)(pt 16 32))

|

||||

)

|

||||

(port

|

||||

(pt 0 48)

|

||||

(input)

|

||||

(text "rst" (rect 0 0 15 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "rst" (rect 21 43 36 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 48)(pt 16 48))

|

||||

)

|

||||

(port

|

||||

(pt 0 64)

|

||||

(input)

|

||||

(text "A[31:0]" (rect 0 0 44 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "A[31:0]" (rect 21 59 65 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 64)(pt 16 64))

|

||||

)

|

||||

(port

|

||||

(pt 0 80)

|

||||

(input)

|

||||

(text "B[31:0]" (rect 0 0 44 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "B[31:0]" (rect 21 75 65 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 80)(pt 16 80))

|

||||

)

|

||||

(port

|

||||

(pt 0 96)

|

||||

(input)

|

||||

(text "ALUOp[4:0]" (rect 0 0 70 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUOp[4:0]" (rect 21 91 91 110)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 96)(pt 16 96))

|

||||

)

|

||||

(port

|

||||

(pt 0 112)

|

||||

(input)

|

||||

(text "shamt[4:0]" (rect 0 0 64 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "shamt[4:0]" (rect 21 107 85 126)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 112)(pt 16 112))

|

||||

)

|

||||

(port

|

||||

(pt 0 128)

|

||||

(input)

|

||||

(text "Hi_in[31:0]" (rect 0 0 67 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "Hi_in[31:0]" (rect 21 123 88 142)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 128)(pt 16 128))

|

||||

)

|

||||

(port

|

||||

(pt 0 144)

|

||||

(input)

|

||||

(text "Lo_in[31:0]" (rect 0 0 68 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "Lo_in[31:0]" (rect 21 139 89 158)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 144)(pt 16 144))

|

||||

)

|

||||

(port

|

||||

(pt 0 160)

|

||||

(input)

|

||||

(text "SpcRegWriteEn" (rect 0 0 90 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "SpcRegWriteEn" (rect 21 155 111 174)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 160)(pt 16 160))

|

||||

)

|

||||

(port

|

||||

(pt 224 32)

|

||||

(output)

|

||||

(text "ALUCond" (rect 0 0 55 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUCond" (rect 148 27 203 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 224 32)(pt 208 32))

|

||||

)

|

||||

(port

|

||||

(pt 224 48)

|

||||

(output)

|

||||

(text "ALURes[31:0]" (rect 0 0 82 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALURes[31:0]" (rect 121 43 203 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 224 48)(pt 208 48))

|

||||

)

|

||||

(port

|

||||

(pt 224 64)

|

||||

(output)

|

||||

(text "ALUHi[31:0]" (rect 0 0 74 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUHi[31:0]" (rect 129 59 203 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 224 64)(pt 208 64))

|

||||

)

|

||||

(port

|

||||

(pt 224 80)

|

||||

(output)

|

||||

(text "ALULo[31:0]" (rect 0 0 75 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALULo[31:0]" (rect 128 75 203 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 224 80)(pt 208 80))

|

||||

)

|

||||

(drawing

|

||||

(rectangle (rect 16 16 208 176))

|

||||

)

|

||||

)

|

||||

214

Quartus Diagram/CONTROL.bdf

Normal file

214

Quartus Diagram/CONTROL.bdf

Normal file

|

|

@ -0,0 +1,214 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "graphic" (version "1.4"))

|

||||

(pin

|

||||

(input)

|

||||

(rect 112 160 280 176)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUCond" (rect 5 0 49 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 120 104 288 120)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "Instr[31:0]" (rect 5 0 55 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 744 248 920 264)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "MemRead" (rect 90 0 139 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 760 648 936 664)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "MemWrite" (rect 90 0 140 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 776 800 952 816)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "RegWrite" (rect 90 0 134 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 776 896 952 912)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "SpcRegWriteEn" (rect 90 0 163 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 760 88 936 104)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "RegDst[1:0]" (rect 90 0 145 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 744 152 920 168)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "PC[1:0]" (rect 90 0 125 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 744 432 920 448)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUOp[4:0]" (rect 90 0 145 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 736 544 912 560)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "shamt[4:0]" (rect 90 0 140 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 760 720 936 736)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "ALUSrc[1:0]" (rect 90 0 145 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 752 328 928 344)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "MemtoReg[2:0]" (rect 90 0 164 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

114

Quartus Diagram/CONTROL.bsf

Normal file

114

Quartus Diagram/CONTROL.bsf

Normal file

|

|

@ -0,0 +1,114 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "symbol" (version "1.2"))

|

||||

(symbol

|

||||

(rect 16 16 224 240)

|

||||

(text "CONTROL" (rect 5 0 47 10)(font "Tahoma" (font_size 6)))

|

||||

(text "inst" (rect 8 203 24 220)(font "Intel Clear" ))

|

||||

(port

|

||||

(pt 0 32)

|

||||

(input)

|

||||

(text "Instr[31:0]" (rect 0 0 62 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "Instr[31:0]" (rect 21 27 83 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 32)(pt 16 32))

|

||||

)

|

||||

(port

|

||||

(pt 0 48)

|

||||

(input)

|

||||

(text "ALUCond" (rect 0 0 55 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUCond" (rect 21 43 76 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 48)(pt 16 48))

|

||||

)

|

||||

(port

|

||||

(pt 208 32)

|

||||

(output)

|

||||

(text "RegDst[1:0]" (rect 0 0 70 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "RegDst[1:0]" (rect 117 27 187 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 32)(pt 192 32))

|

||||

)

|

||||

(port

|

||||

(pt 208 48)

|

||||

(output)

|

||||

(text "PC[1:0]" (rect 0 0 44 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "PC[1:0]" (rect 143 43 187 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 48)(pt 192 48))

|

||||

)

|

||||

(port

|

||||

(pt 208 64)

|

||||

(output)

|

||||

(text "MemRead" (rect 0 0 60 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "MemRead" (rect 127 59 187 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 64)(pt 192 64))

|

||||

)

|

||||

(port

|

||||

(pt 208 80)

|

||||

(output)

|

||||

(text "MemtoReg[2:0]" (rect 0 0 92 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "MemtoReg[2:0]" (rect 95 75 187 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 80)(pt 192 80))

|

||||

)

|

||||

(port

|

||||

(pt 208 96)

|

||||

(output)

|

||||

(text "ALUOp[4:0]" (rect 0 0 70 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUOp[4:0]" (rect 117 91 187 110)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 96)(pt 192 96))

|

||||

)

|

||||

(port

|

||||

(pt 208 112)

|

||||

(output)

|

||||

(text "shamt[4:0]" (rect 0 0 64 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "shamt[4:0]" (rect 123 107 187 126)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 112)(pt 192 112))

|

||||

)

|

||||

(port

|

||||

(pt 208 128)

|

||||

(output)

|

||||

(text "MemWrite" (rect 0 0 61 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "MemWrite" (rect 126 123 187 142)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 128)(pt 192 128))

|

||||

)

|

||||

(port

|

||||

(pt 208 144)

|

||||

(output)

|

||||

(text "ALUSrc[1:0]" (rect 0 0 71 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "ALUSrc[1:0]" (rect 116 139 187 158)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 144)(pt 192 144))

|

||||

)

|

||||

(port

|

||||

(pt 208 160)

|

||||

(output)

|

||||

(text "RegWrite" (rect 0 0 54 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "RegWrite" (rect 133 155 187 174)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 160)(pt 192 160))

|

||||

)

|

||||

(port

|

||||

(pt 208 176)

|

||||

(output)

|

||||

(text "SpcRegWriteEn" (rect 0 0 90 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "SpcRegWriteEn" (rect 97 171 187 190)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 208 176)(pt 192 176))

|

||||

)

|

||||

(drawing

|

||||

(rectangle (rect 16 16 192 208))

|

||||

)

|

||||

)

|

||||

1219

Quartus Diagram/MIPS_CPU_Diagram.bdf

Normal file

1219

Quartus Diagram/MIPS_CPU_Diagram.bdf

Normal file

File diff suppressed because it is too large

Load diff

BIN

Quartus Diagram/MIPS_CPU_Diagram.psd

Normal file

BIN

Quartus Diagram/MIPS_CPU_Diagram.psd

Normal file

Binary file not shown.

31

Quartus Diagram/MIPS_CPU_Diagram.qpf

Normal file

31

Quartus Diagram/MIPS_CPU_Diagram.qpf

Normal file

|

|

@ -0,0 +1,31 @@

|

|||

# -------------------------------------------------------------------------- #

|

||||

#

|

||||

# Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

# Your use of Intel Corporation's design tools, logic functions

|

||||

# and other software and tools, and any partner logic

|

||||

# functions, and any output files from any of the foregoing

|

||||

# (including device programming or simulation files), and any

|

||||

# associated documentation or information are expressly subject

|

||||

# to the terms and conditions of the Intel Program License

|

||||

# Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

# the Intel FPGA IP License Agreement, or other applicable license

|

||||

# agreement, including, without limitation, that your use is for

|

||||

# the sole purpose of programming logic devices manufactured by

|

||||

# Intel and sold by Intel or its authorized distributors. Please

|

||||

# refer to the applicable agreement for further details, at

|

||||

# https://fpgasoftware.intel.com/eula.

|

||||

#

|

||||

# -------------------------------------------------------------------------- #

|

||||

#

|

||||

# Quartus Prime

|

||||

# Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition

|

||||

# Date created = 16:10:59 December 17, 2020

|

||||

#

|

||||

# -------------------------------------------------------------------------- #

|

||||

|

||||

QUARTUS_VERSION = "19.1"

|

||||

DATE = "16:10:59 December 17, 2020"

|

||||

|

||||

# Revisions

|

||||

|

||||

PROJECT_REVISION = "MIPS_CPU_Diagram"

|

||||

54

Quartus Diagram/MIPS_CPU_Diagram.qsf

Normal file

54

Quartus Diagram/MIPS_CPU_Diagram.qsf

Normal file

|

|

@ -0,0 +1,54 @@

|

|||

# -------------------------------------------------------------------------- #

|

||||

#

|

||||

# Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

# Your use of Intel Corporation's design tools, logic functions

|

||||

# and other software and tools, and any partner logic

|

||||

# functions, and any output files from any of the foregoing

|

||||

# (including device programming or simulation files), and any

|

||||

# associated documentation or information are expressly subject

|

||||

# to the terms and conditions of the Intel Program License

|

||||

# Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

# the Intel FPGA IP License Agreement, or other applicable license

|

||||

# agreement, including, without limitation, that your use is for

|

||||

# the sole purpose of programming logic devices manufactured by

|

||||

# Intel and sold by Intel or its authorized distributors. Please

|

||||

# refer to the applicable agreement for further details, at

|

||||

# https://fpgasoftware.intel.com/eula.

|

||||

#

|

||||

# -------------------------------------------------------------------------- #

|

||||

#

|

||||

# Quartus Prime

|

||||

# Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition

|

||||

# Date created = 16:10:59 December 17, 2020

|

||||

#

|

||||

# -------------------------------------------------------------------------- #

|

||||

#

|

||||

# Notes:

|

||||

#

|

||||

# 1) The default values for assignments are stored in the file:

|

||||

# MIPS_CPU_Diagram_assignment_defaults.qdf

|

||||

# If this file doesn't exist, see file:

|

||||

# assignment_defaults.qdf

|

||||

#

|

||||

# 2) Altera recommends that you do not modify this file. This

|

||||

# file is updated automatically by the Quartus Prime software

|

||||

# and any changes you make may be lost or overwritten.

|

||||

#

|

||||

# -------------------------------------------------------------------------- #

|

||||

|

||||

|

||||

set_global_assignment -name FAMILY "Cyclone IV E"

|

||||

set_global_assignment -name DEVICE auto

|

||||

set_global_assignment -name TOP_LEVEL_ENTITY MIPS_CPU_Diagram

|

||||

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 19.1.0

|

||||

set_global_assignment -name PROJECT_CREATION_TIME_DATE "16:10:59 DECEMBER 17, 2020"

|

||||

set_global_assignment -name LAST_QUARTUS_VERSION "19.1.0 Lite Edition"

|

||||

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

|

||||

set_global_assignment -name BDF_FILE MIPS_CPU_Diagram.bdf

|

||||

set_global_assignment -name BDF_FILE ALU.bdf

|

||||

set_global_assignment -name BDF_FILE CONTROL.bdf

|

||||

set_global_assignment -name BDF_FILE PC.bdf

|

||||

set_global_assignment -name BDF_FILE REGISTERS.bdf

|

||||

set_global_assignment -name BDF_FILE MUX_RegDst.bdf

|

||||

set_global_assignment -name BDF_FILE MUX_MemtoREg.bdf

|

||||

set_global_assignment -name BDF_FILE MUX_ALUSrc.bdf

|

||||

BIN

Quartus Diagram/MIPS_CPU_Diagram.qws

Normal file

BIN

Quartus Diagram/MIPS_CPU_Diagram.qws

Normal file

Binary file not shown.

102

Quartus Diagram/MUX_ALUSrc.bdf

Normal file

102

Quartus Diagram/MUX_ALUSrc.bdf

Normal file

|

|

@ -0,0 +1,102 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "graphic" (version "1.4"))

|

||||

(pin

|

||||

(input)

|

||||

(rect 400 312 568 328)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "0" (rect 5 0 10 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 408 384 576 400)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "1" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 392 528 560 544)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "2" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 432 176 600 192)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "sel[1:0]" (rect 5 0 42 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 704 264 880 280)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "output" (rect 90 0 120 17)(font "Intel Clear" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

65

Quartus Diagram/MUX_ALUSrc.bsf

Normal file

65

Quartus Diagram/MUX_ALUSrc.bsf

Normal file

|

|

@ -0,0 +1,65 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "symbol" (version "1.2"))

|

||||

(symbol

|

||||

(rect 16 16 112 144)

|

||||

(text "MUX_ALUSrc" (rect 5 0 58 10)(font "Tahoma" (font_size 6)))

|

||||

(text "inst" (rect 8 107 24 124)(font "Intel Clear" ))

|

||||

(port

|

||||

(pt 0 32)

|

||||

(input)

|

||||

(text "sel" (rect 0 0 16 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "sel" (rect 21 27 37 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 32)(pt 16 32))

|

||||

)

|

||||

(port

|

||||

(pt 0 48)

|

||||

(input)

|

||||

(text "0" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "0" (rect 21 43 29 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 48)(pt 16 48))

|

||||

)

|

||||

(port

|

||||

(pt 0 64)

|

||||

(input)

|

||||

(text "1" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "1" (rect 21 59 29 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 64)(pt 16 64))

|

||||

)

|

||||

(port

|

||||

(pt 0 80)

|

||||

(input)

|

||||

(text "2" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "2" (rect 21 75 29 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 80)(pt 16 80))

|

||||

)

|

||||

(port

|

||||

(pt 96 32)

|

||||

(output)

|

||||

(text "output" (rect 0 0 38 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "output" (rect 37 27 75 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 96 32)(pt 80 32))

|

||||

)

|

||||

(drawing

|

||||

(rectangle (rect 16 16 80 112))

|

||||

)

|

||||

)

|

||||

134

Quartus Diagram/MUX_MemtoReg.bdf

Normal file

134

Quartus Diagram/MUX_MemtoReg.bdf

Normal file

|

|

@ -0,0 +1,134 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "graphic" (version "1.4"))

|

||||

(pin

|

||||

(input)

|

||||

(rect 360 112 528 128)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "sel[2:0]" (rect 5 0 42 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 344 184 512 200)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "0" (rect 5 0 11 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 344 280 512 296)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "1" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 344 400 512 416)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "2" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 344 560 512 576)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "3" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 336 752 504 768)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "4" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 728 408 904 424)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "output" (rect 90 0 120 12)(font "Arial" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

79

Quartus Diagram/MUX_MemtoReg.bsf

Normal file

79

Quartus Diagram/MUX_MemtoReg.bsf

Normal file

|

|

@ -0,0 +1,79 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "symbol" (version "1.2"))

|

||||

(symbol

|

||||

(rect 16 16 152 176)

|

||||

(text "MUX_MemtoReg" (rect 5 0 72 10)(font "Tahoma" (font_size 6)))

|

||||

(text "inst" (rect 8 139 24 156)(font "Intel Clear" ))

|

||||

(port

|

||||

(pt 0 32)

|

||||

(input)

|

||||

(text "sel[2:0]" (rect 0 0 44 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "sel[2:0]" (rect 21 27 65 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 32)(pt 16 32))

|

||||

)

|

||||

(port

|

||||

(pt 0 48)

|

||||

(input)

|

||||

(text "0" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "0" (rect 21 43 29 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 48)(pt 16 48))

|

||||

)

|

||||

(port

|

||||

(pt 0 64)

|

||||

(input)

|

||||

(text "1" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "1" (rect 21 59 29 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 64)(pt 16 64))

|

||||

)

|

||||

(port

|

||||

(pt 0 80)

|

||||

(input)

|

||||

(text "2" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "2" (rect 21 75 29 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 80)(pt 16 80))

|

||||

)

|

||||

(port

|

||||

(pt 0 96)

|

||||

(input)

|

||||

(text "3" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "3" (rect 21 91 29 110)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 96)(pt 16 96))

|

||||

)

|

||||

(port

|

||||

(pt 0 112)

|

||||

(input)

|

||||

(text "4" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "4" (rect 21 107 29 126)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 112)(pt 16 112))

|

||||

)

|

||||

(port

|

||||

(pt 136 32)

|

||||

(output)

|

||||

(text "output" (rect 0 0 38 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "output" (rect 77 27 115 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 136 32)(pt 120 32))

|

||||

)

|

||||

(drawing

|

||||

(rectangle (rect 16 16 120 144))

|

||||

)

|

||||

)

|

||||

102

Quartus Diagram/MUX_RegDst.bdf

Normal file

102

Quartus Diagram/MUX_RegDst.bdf

Normal file

|

|

@ -0,0 +1,102 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "graphic" (version "1.4"))

|

||||

(pin

|

||||

(input)

|

||||

(rect 264 160 432 176)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "sel[1:0]" (rect 5 0 40 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 232 248 400 264)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "0" (rect 5 0 11 12)(font "Arial" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 248 336 416 352)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "1" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(input)

|

||||

(rect 248 432 416 448)

|

||||

(text "INPUT" (rect 125 0 153 10)(font "Arial" (font_size 6)))

|

||||

(text "2" (rect 5 0 11 17)(font "Intel Clear" ))

|

||||

(pt 168 8)

|

||||

(drawing

|

||||

(line (pt 84 12)(pt 109 12))

|

||||

(line (pt 84 4)(pt 109 4))

|

||||

(line (pt 113 8)(pt 168 8))

|

||||

(line (pt 84 12)(pt 84 4))

|

||||

(line (pt 109 4)(pt 113 8))

|

||||

(line (pt 109 12)(pt 113 8))

|

||||

)

|

||||

(text "VCC" (rect 128 7 148 17)(font "Arial" (font_size 6)))

|

||||

)

|

||||

(pin

|

||||

(output)

|

||||

(rect 640 280 816 296)

|

||||

(text "OUTPUT" (rect 1 0 39 10)(font "Arial" (font_size 6)))

|

||||

(text "output" (rect 90 0 120 12)(font "Arial" ))

|

||||

(pt 0 8)

|

||||

(drawing

|

||||

(line (pt 0 8)(pt 52 8))

|

||||

(line (pt 52 4)(pt 78 4))

|

||||

(line (pt 52 12)(pt 78 12))

|

||||

(line (pt 52 12)(pt 52 4))

|

||||

(line (pt 78 4)(pt 82 8))

|

||||

(line (pt 82 8)(pt 78 12))

|

||||

(line (pt 78 12)(pt 82 8))

|

||||

)

|

||||

)

|

||||

65

Quartus Diagram/MUX_RegDst.bsf

Normal file

65

Quartus Diagram/MUX_RegDst.bsf

Normal file

|

|

@ -0,0 +1,65 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||

functions, and any output files from any of the foregoing

|

||||

(including device programming or simulation files), and any

|

||||

associated documentation or information are expressly subject

|

||||

to the terms and conditions of the Intel Program License

|

||||

Subscription Agreement, the Intel Quartus Prime License Agreement,

|

||||

the Intel FPGA IP License Agreement, or other applicable license

|

||||

agreement, including, without limitation, that your use is for

|

||||

the sole purpose of programming logic devices manufactured by

|

||||

Intel and sold by Intel or its authorized distributors. Please

|

||||

refer to the applicable agreement for further details, at

|

||||

https://fpgasoftware.intel.com/eula.

|

||||

*/

|

||||

(header "symbol" (version "1.2"))

|

||||

(symbol

|

||||

(rect 16 16 152 144)

|

||||

(text "MUX_RegDst" (rect 5 0 58 10)(font "Tahoma" (font_size 6)))

|

||||

(text "inst" (rect 8 107 24 124)(font "Intel Clear" ))

|

||||

(port

|

||||

(pt 0 32)

|

||||

(input)

|

||||

(text "sel[1:0]" (rect 0 0 44 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "sel[1:0]" (rect 21 27 65 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 32)(pt 16 32))

|

||||

)

|

||||

(port

|

||||

(pt 0 48)

|

||||

(input)

|

||||

(text "0" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "0" (rect 21 43 29 62)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 48)(pt 16 48))

|

||||

)

|

||||

(port

|

||||

(pt 0 64)

|

||||

(input)

|

||||

(text "1" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "1" (rect 21 59 29 78)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 64)(pt 16 64))

|

||||

)

|

||||

(port

|

||||

(pt 0 80)

|

||||

(input)

|

||||

(text "2" (rect 0 0 8 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "2" (rect 21 75 29 94)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 0 80)(pt 16 80))

|

||||

)

|

||||

(port

|

||||

(pt 136 32)

|

||||

(output)

|

||||

(text "output" (rect 0 0 38 19)(font "Intel Clear" (font_size 8)))

|

||||

(text "output" (rect 77 27 115 46)(font "Intel Clear" (font_size 8)))

|

||||

(line (pt 136 32)(pt 120 32))

|

||||

)

|

||||

(drawing

|

||||

(rectangle (rect 16 16 120 112))

|

||||

)

|

||||

)

|

||||

134

Quartus Diagram/PC.bdf

Normal file

134

Quartus Diagram/PC.bdf

Normal file

|

|

@ -0,0 +1,134 @@

|

|||

/*

|

||||

WARNING: Do NOT edit the input and output ports in this file in a text

|

||||

editor if you plan to continue editing the block that represents it in

|

||||

the Block Editor! File corruption is VERY likely to occur.

|

||||

*/

|

||||

/*

|

||||

Copyright (C) 2019 Intel Corporation. All rights reserved.

|

||||

Your use of Intel Corporation's design tools, logic functions

|

||||

and other software and tools, and any partner logic

|

||||